Embedded Systems Pricing

How much will it cost and how long will it take?

The bulk of our engagements fall between $10K – $120K and last ~2 – 6 months.

There are obviously outliers in both directions. Both the cost and the duration are typically proportional to the size of the effort. We’re not hobbyists.

Here’s some general examples to start to give you a feel.

Scenario |

Cost |

Duration |

|---|---|---|

| PCB Layout Services with optional Signal Integrity analysis and optimization | ~$5K to $35K | ~ 1 to 8 weeks |

| Low to medium complexity microcontroller-based boardschematic design & PCB layout and firmware development | ~$25K to $50K | ~ 6 to 12 weeks |

| FPGA VHDL development | ~$15K to $125K | ~1 to 6+ months |

| Firmware / software development | ~$10K to $125K | ~2 weeks to 6+ months |

| Schematic and/or PCB Layout peer review (w/ summary of analysis and findings report) | ~$5K to $15K | ~ 1 to 3 weeks |

| System EMC assessment (w/ summary report including root cause analysis and recommended countermeasures) | ~$5K to $20K | ~ 1 to 4 weeks |

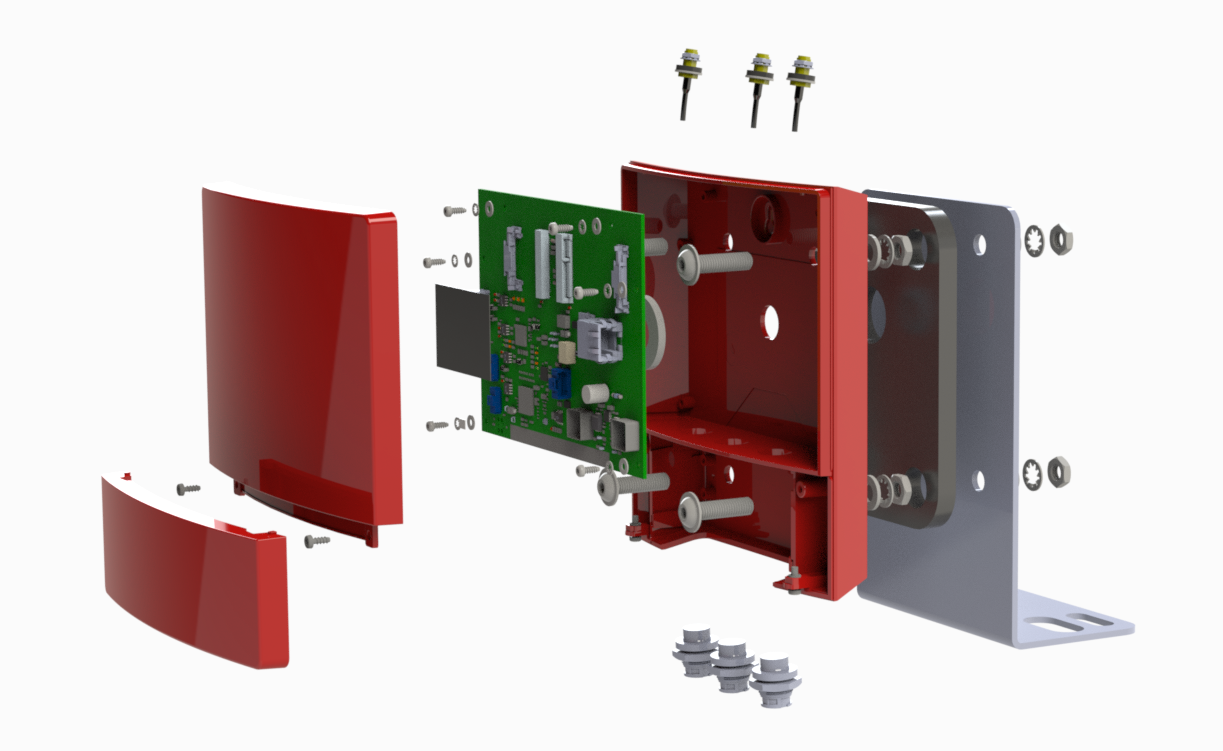

| Semi Custom Mechanical Enclosure Design (Customization of off the shelf enclosure) in parallel with board design | ~$3K to $5K | ~2 to 12 weeks |

| Fully Custom Mechanical Enclosure Design in parallel with board design | ~$5K to $10K | ~4 to 12 weeks |

| Phase 0 – Requirements generation, architecture, analysis of alternatives, cost estimation (for a typical medium-complexity system) | ~$5K to $10K | ~1 to 2 weeks |

What a few of our clients have to say

Please pass along my thanks and appreciation to the AppliedLogix folks for pulling this one out of the fire… This is going to be big – you can’t believe the response. Product is dead-on for first generation.

A.L.’s capacity to frame and follow through on complex assignments is frighteningly good! I wish I could say it’s just youthful energy but you guys aren’t that young either. It’s very valuable.

We could never have done this without you pulling it together for us.

AppliedLogix has earned special recognition… the driving force behind the architecture specification, detailed design, PWB layout, and prototype design validation of this high-performance image path subsystem.

AppliedLogix’ commitment to quality and robustness has been a significant contributor to the success of our project.

The new layout for the AVDD power planes is excellent – great job of maximizing the clearance to critical input nodes… Very well thought out and executed… You should be proud of this work! Ship it!

Thanks for all you do to keep us moving in the right direction! Really appreciate how tightly run the AppliedLogix ship is.

You Nailed It.

…There are many high power / high current PWM channels and the critical low noise signals are perfectly quiet, there is no discernible noise at all. The layout is extraordinary – well done AppliedLogix!

Great news…my new boards arrived today and the DDR3 calibration and self-test passes right out of the box with flying colors – thanks for your help!